前几日,设计中突然觉着需要一个电路,在外来一个脉冲后,能输出唯一的一个宽度为系统时钟周期的脉冲,竟不知此为所谓脉冲发生器。思索几日,亦有一得如下,

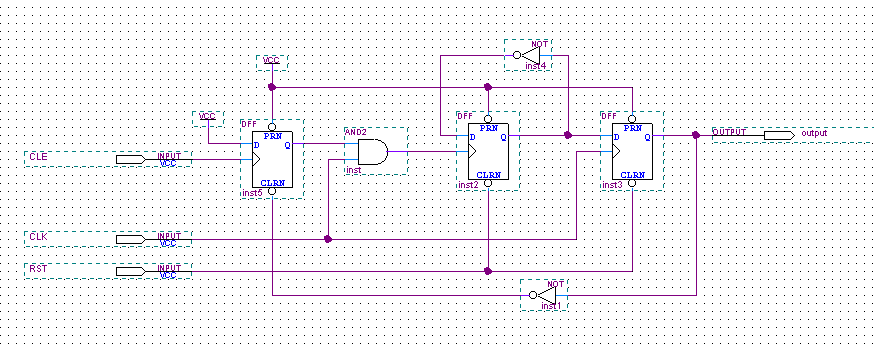

原理图:

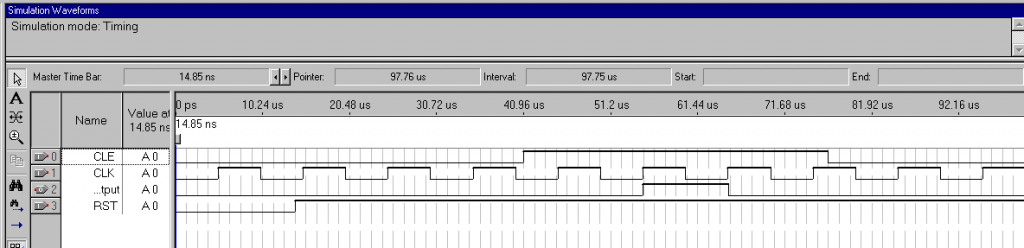

仿真波形:

若要想输出提前一个时钟周期,可以取原理图中间的D触发器的Q端为输出。

这个电路有一个死锁态,就是初始态时第一个D触发器输出为零,而第二个D触发器输出为1的状态,所以图中特意加入了复位信号。

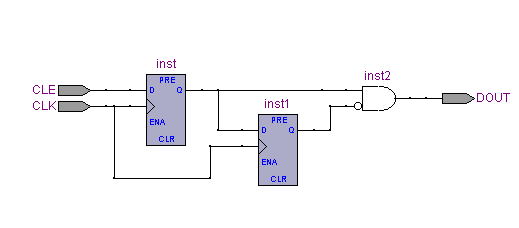

今日上网,偶及某君Blog,更有简洁办法:

详细资料请参考(http://blog.ednchina.com/chactor/193654/message.aspx)

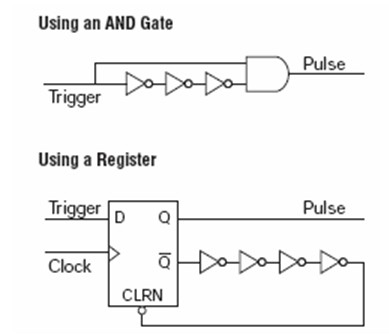

更有异步方法:

上图中,第一个方法可以在Trigger输入一个脉冲后,无论长短,只输出一个窄脉冲,但是限于非门延时,输出脉冲宽度比较小,在某些场合并不能作为稳定的触发源,第二个电路,愚以为是错误的,在Trigger持续高电平期间,此电路会一直输出脉冲。